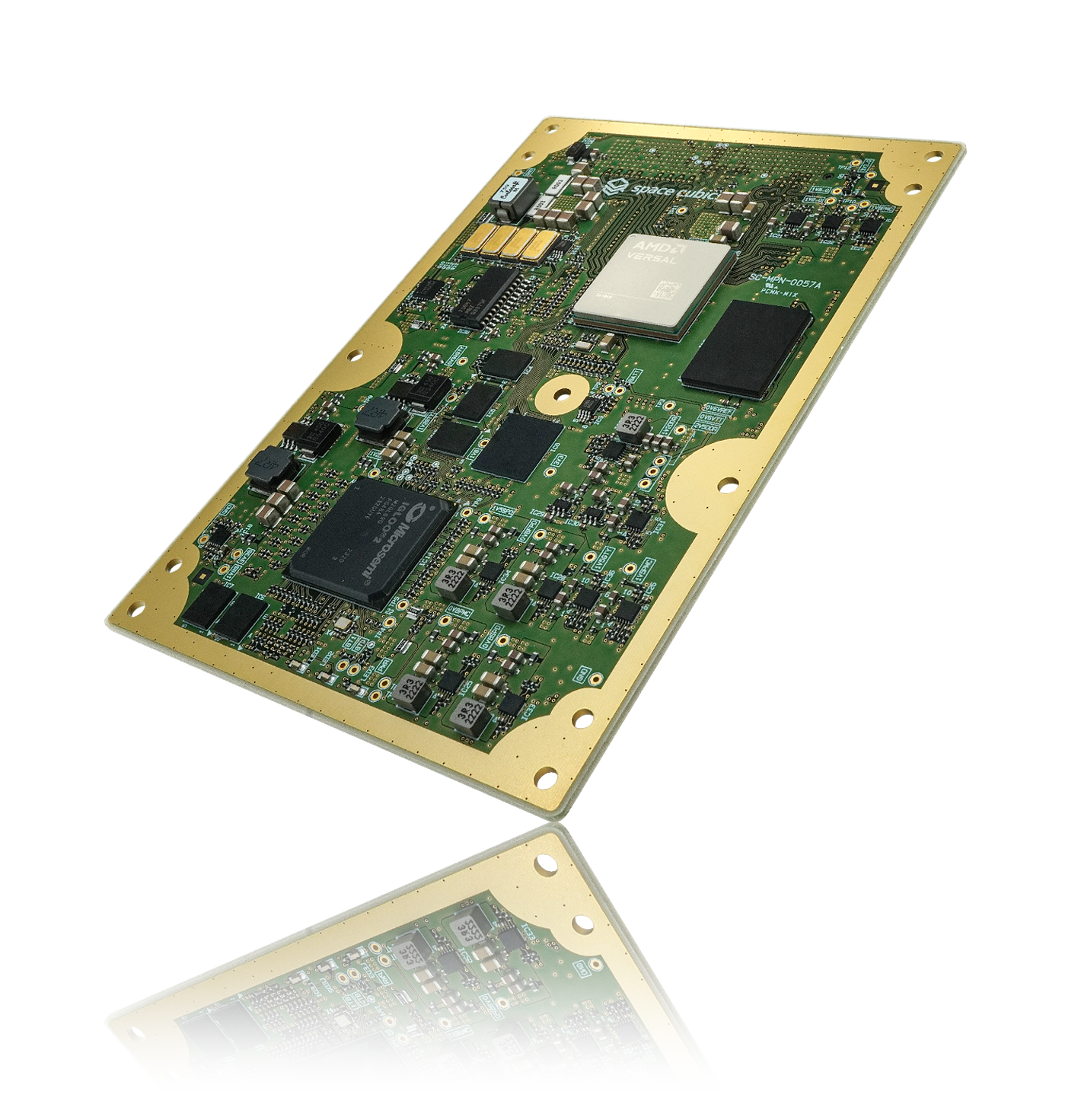

SC-OBC MODULE V1

High-End Space Grade On-board Computer (2026年春発売予定)

OVERVIEW

New Space向けハイエンドコンピュータモジュール

SC-OBC Module V1

CPU・FPGA・AI Engineを統合したヘテロジニアスプラットフォームコンピューティング (Adaptive SoC)を採用した AMD Versalを搭載する高性能オンボードコンピュータです。光学センサーや SAR・LiDARなどから入力される大容量のセンサーデータに対し、入力処理・ハードウェアアクセサレーションやベクトル演算を伴うエッジ処理、大容量ストレージへの記録を、効率的に実行することができます。

USE CASES

- 地球観測用センサ(SAR, LiDAR)の高速データ処理

- 誘導航法制御(GNC)

- 地球周回衛星、静止軌道衛星、月周回・着陸・探査ミッション

SPECS

1. Main Processor

Device

AMD Versal AI Edge Series VE2302

Application Processor

Dual core Arm Cortex-A72 Up to 1.3 GHz (48 KByte/32 KByte L1 Cache w/ parity & ECC, 1 MByte L2 Cache w/ ECC)

Real-Time Processor

Dual core Arm Cortex-R5F Up to 600 MHz (32 KByte/32 KByte L1 Cache, 256 KByte TCM w/ ECC)

AI Engine

AI Engine-ML Tile: 34, AIE/AIE-ML Data Memory Mbit: 17, AIE-ML Shared Memory Mbit: 68

Programmable Logic

System Logic: 328,720, LUTs: 150,272, DSP Engines: 464, Total Block RAM: 5.4 Mbit, UltraRAM: 43,6 Mbit, Accelerator RAM: 32 Mbit

2. Safety Processor

Device

Microchip IGLOO2

3. Memory

DDR4

Rad-tolerant DDR4 memory w/ ECC 4 GByte

Boot Memory

NOR Flash 64 MByte (Redundancy)

eMMC

64 GByte

High Reliability Memory

FRAM 1 MByte × 2

4. Pre-Installed Operating System

APU

Linux

RPU

Zephyr RTOS

5. Board to Board Interface (User IO)

Versal MIO

Platform Management MIO: 27 signals, Low Power Domain MIO: 26 signals, Selectable Interface: Gigabit EtherMAC, USB2.0 (ULPI), UART, I2C, SPI, GPIO, CAN FD, SD/eMMC

Versal PL XPIO

54 signals (VDDIO: 1.0/1.2/1.35/1.5 V)

Versal GTYP

40 signals / Clock 4 pair / TX 8 pair / RX 8 pair

IGLOO2 MSIO

48 signals (VDDIO 1.2/1.5/1.8/2.5/3.3 V)

6. Board Health Function

On-Board Sensor

Temperature Sensor, Current/Voltage Monitor

Power Management

Over-current detection, Brownout protection

7. Environmental Characteristics

Power Supply

DC 5.0 V (20 - 40 W typical)

Operating Temperature

-40 〜 80 ℃

Size

100 mm × 150 mm

PRICE

SC-OBC Module V1

2026年春発売予定

SC-OBC Module V1は2026年春の発売を予定しています。詳しくは お問い合わせフォーム よりお問い合わせください。

DEV KIT

開発キット

coming soon

オプション品

coming soon

DOCUMENTS

This document provides the technical information required to develop the FPGA design for the SC-OBC Module V1.